# Equipamiento de Circuito Electrónicos

22 736 4461 / 22 728 6162 systelec@systelec.cl

22 736 3650 / 22 736 5827

ww.svstelec.cl

**(**+56 9 34415419

# Av. Pedro Fontova 3954

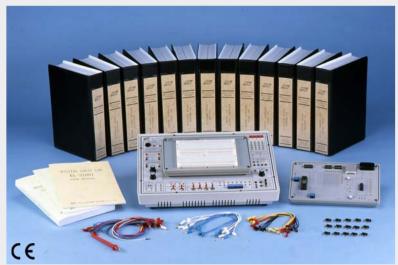

## KL-300

# Laboratorio de Lógica Digital

El KL-300 laboratorio de lógica digital es un sistema comprensivo y autónomo, adecuado para todo tipo de persona que se dedica a experimentos de lógica digital.

Todos los equipos necesarios para los experimentos de lógica digital están instalado en la unidad principal, como fuente de alimentación, generador de señal, interruptores y visualizador.

Los 13 módulos cubren una amplia variedad de tópicos esenciales en el campo de lógica digital. Este es un sistema de bajo costo y ahorro de tiempo para estudiantes e investigadores interesado en el desarrollo y pruebas de prototipos de circuitos.

#### Características

- 1. Adecuado para la combinación lógica, secuencial lógica y diseño de circuito de microprocesador y experimentos.

- 2. Herramienta ideal para el aprendizaje de circuito lógica digital básica.

- 3. Potencia comprensivo, fuente de señal y dispositivo de prueba para experimentos convenientes.

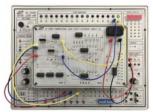

- 4. Los experimentos son expandibles y flexibles con breadboard

- 5. Capaz de procesar circuitos TTL, CMOS, NMOS, PMOS y ECL.

- 6. Todas las unidades de fuentes están equipados con protección de sobrecarga para mayor seguridad.

- 7. Todos los módulos están equipado con un interruptor DIP de 8 bit para la simulación de falla.

- 8. Caja individual de todos los módulos para facilitar el almacenamiento y el transporte.

- 9. Todos los generadores de señales tienen terminales de salida de nivel TTL y CMOS independientes y simultáneos.

- 10. Incluido entrenamiento basado en computadora.

### Especificaciones

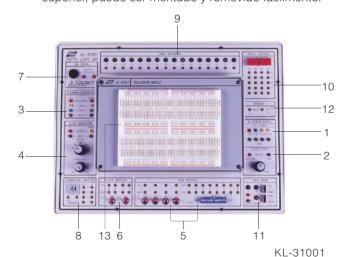

#### Unidad Principal (KL-31001)

- 1. Fuente de Alimentación CD Dual

- (1) Rango de voltaje: +5V, 1.5A; -5V, 0.3A;

±12V, 0.3A

- (2) Con salida de protección de sobrecarga

- 2. Fuente de Alimentación CD Ajustable

- (1) Rango de voltaje: +1.5V~+15V

- (2) Salida de corriente máxima: 0.5A

- (3) Con salida de protección de sobrecarga

- 3. Frecuencia Estándar

- (1) Frecuencia: 1MHz, 60Hz, 1Hz

- (2) Precisión: ±0.01% (1MHz)

- (3) Salida de viento: 10 TTL de carga

- 4. Generador de señal de reloj

- (1) Frecuencia: 1Hz-1MHz (6 rangos)

a. 1Hz ~ 10Hz d. 1KHz ~ 10KHz

b. 10Hz ~ 100Hz e. 10KHz ~ 100KHz

c. 100Hz ~ 1KHz f. 100KHz ~ 1MHz

(2) Salida de viento : 10 TTL de carga

5. Interruptor de Datos

- (1) Interruptor DIP de 8 bits x 2, nivel de salida TTL de 16 bit

- (2) Interruptor de palanca x 4, cada uno contiene circuito **DEBOUNCE**

- (3) Salida de viento: 10 TTL de carga

22 736 4461 / 22 728 6162 systelec@systelec.cl

ww.systelec.cl

22 736 3650 / 22 736 5827

**(**+56 9 34415419 Av. Pedro Fontova 3954 Santiago de Chile

- 6. Interruptor de Pulso

- (1) 2 juegos de salida de control independiente

- (2) Cada juego contiene Q, salida de  $\overline{Q}$ , ancho de pulso > 5ms

- (3) Cada juego de interruptor contiene circuito DEBOUNCE

- (4) Salida de viento : 10 TTL de carga

- 7. Generador de Seña Lineal

- (1) Frecuencia: 50 / 60Hz

- (2) Salida de voltaje : 6Vrms

- (3) Con protección de sobrecarga

- 8. Interruptor Thumbwheel

- 2 dígitos, salida de código BDC y entrada de punto común

- 9. Indicador Lógico

- (1) 16 juegos de LED independiente que indican estado lógico alto y bajo

- (2) Impedancia de entrada : ≥ 100KΩ

- 10. Pantalla Digital

- (1) 4 juegos de visualizador LED de 7 segmentos independiente

- (2) Con BCD, decodificador / operador (driver) de 7 segmentos y entrada de DP

- (3) Entrada con código 8-4-2-1

- 11. Prueba Lógica

- (1) Nivel TTL y CMOS

- (2) Visualizador LED 5 mm

- (3) Visualizador LED muestra estado lógico bajo "Lo" y alto "Hi" respectivamente

- 12. Bocina

Una bocina de 8Ω, 0.25W con circuito operador (driver)

13. Módulos de Breadboard (AC-90001) Breadboard con 1680 puntos de conexión en el panel superior, puede ser montado y removido fácilmente.

#### Módulos de Experimento

- 1. Los 13 módulos están equipados con interruptores DIP de 8-bit para la simulación de fallas. El usuario podrá aprender varios soluciones de problemas a través del ajuste de interruptor DIP en diferente posiciones.

- 2. Las soluciones para todas las fallas están listadas en el manual de experimentos para la referencia de los usuarios.

- 3. En la unidad principal y todos los modulos se utilizan enchufes y tomas de 2 mm.

- 4. Manual comprensivo de experimentos y del instructor.

- 5. Dimensión de módulo: 255 x 165 x 30 mm.

- 6. Se utiliza enchufe de conexión en los módulos para prevenir daños accidentales.

- 7. Caja individual de almacenaje para cada módulo.

#### Listado de Módulos

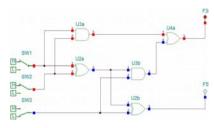

Experimentos de Puerta Lógica Básica

KL-33002 Experimentos de Circuito Lógico Combinado (1)

Experimentos de Circuito Lógico Combinado (2)

KL-33004 Experimentos de Circuito Lógico Combinado (3)

Experimentos de Circuito Lógico Combinado (4)

Experimentos de Circuito Lógico Combinado (5)

KL-33007 Experimentos de Circuito del generador de reloj

Experimentos de Circuito Lógica Secuencial (1)

Experimentos de Circuito Lógica Secuencial (2)

22 736 3650 / 22 736 5827 22 736 4461 / 22 728 6162 systelec@systelec.cl

ww.systelec.cl +56 9 34415419

P+56 9 34415419

Av. Pedro Fontova 3954

Santiago de Chile

KL-33010 Experimentos de Circuito de Memoria (1)

KL-33011 Experimentos de Circuito de Memoria (2)

KL-33012 Experimentos de Circuitos convertidores (1)

KL-33013 Experimentos de Circuitos convertidores (2)

#### Listado de Experimentos

| 1. Experimentos de Puerta Lógica Básica                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------|

| (1) Introducción para puerta lógica e interruptor                                                                                  |

| KL-33001(A)                                                                                                                        |

| (2) Circuitos de puerta lógica                                                                                                     |

| <ul> <li>a. Circuito de lógica de diodos (DL)KL-33001(C)</li> <li>b. Circuito de lógica de resistencia-transistor (RTL)</li> </ul> |

| KL-33001(B)                                                                                                                        |

| c. Circuito de lógica diodo-transistor (DTL)                                                                                       |

| KL-33001(B.C                                                                                                                       |

| d. Circuito de lógica transistor a transistor (TTL)                                                                                |

| KL-33001(D)                                                                                                                        |

| e. Circuito lógica CMOSKL-33001(E)                                                                                                 |

| (3) Medición de voltaje umbral                                                                                                     |

| a. Medición de voltaje umbral TTLKL-33001(D)                                                                                       |

| <ul><li>b. Medición de voltaje umbral CMOSKL-33001(E)</li><li>(4) Medición de voltaje / corriente</li></ul>                        |

| a. Medición de voltaje / corriente TTL de E/S                                                                                      |

| KL-33001(D)                                                                                                                        |

| b. Medición de voltaje / corriente CMOS.KL-33001(E)                                                                                |

| (5) Medición de retardo de transmisión de puerta lógica básic                                                                      |

| a. Medición de tiempo de retardo de puerta TTL                                                                                     |

| KL-33001(D)                                                                                                                        |

| b. Medición de tiempo de retardo de puerta CMOSKL-33001(E)                                                                         |

| (6) Medición de las características de puerta lógica básica                                                                        |

| a. Medición de características de pueta AND                                                                                        |

|                                                                                                                                    |

| b. Medición de características de puerta OR<br>KL-33001(D)                                                                         |

| c. Medición de características de puerta INVERTER                                                                                  |

| KL-33001(D)                                                                                                                        |

| d. Medición de características de puerta NAND                                                                                      |

| KL-33001(D)                                                                                                                        |

| e. Medición de características de puerta NOR                                                                                       |

| KL-33001(D)                                                                                                                        |

| f. Medición de características de puerta XOR                                                                                       |

| KL-33001(D)                                                                                                                        |

|                                                                                                                                    |

| (7) Interface entre la puerta lógica a. Interface de TTL a CMOSKL-33001(D.E)                                          |

|-----------------------------------------------------------------------------------------------------------------------|

| b. Interface de CMOS a TTLKL-33001(D.E)  2. Experimentos del Circuito de Lógica Combinada                             |

| (1) Circuito de puerta NORKL-33002(A)                                                                                 |

| (2) Circuito de puerta NANDKL-33002(B) (3) Circuito de puerta XOR                                                     |

| a. Construcción de puerta XOR con puerta NANDKL-33002(B)                                                              |

| b. Construcción de puerta XOR con puerta básicaKL-33002(C)                                                            |

| (4) Circuito de puerta AND-OR-INVERT (AOI)                                                                            |

| (5) Comparador de circuito                                                                                            |

| a. Comparador construido con puerta lógica básicaKL-33002(C)                                                          |

| b. Comparador construido con TTL ICKL-33002(D)                                                                        |

| (6) Circuito de puerta SchmittKL-33002(A)                                                                             |

| (7) Circuitos de puerta de colector abierto                                                                           |

| a. Circuito de voltaje / corriente altoKL-33002(E)                                                                    |

| b. Construcción de puerta AND con puerta de colector                                                                  |

| abiertoKL-33002(E)                                                                                                    |

| (8) Circuito de puerta tristate                                                                                       |

| <ul><li>a. Medición de tabla de verdadKL-33003(C)</li><li>b. Construcción de puerta AND con puerta tristate</li></ul> |

| KL-33003(C)                                                                                                           |

| c. Circuito de transmisión bidireccionalKL-33003(C)                                                                   |

| (9) Circuito de sumador media y sumador completo                                                                      |

| a. Construcción HA con puerta lógica básica                                                                           |

| KL-33004(A)                                                                                                           |

| b. Circuito de sumador completoKL-33004(B)                                                                            |

| c. Circuito de Generador de acarreo para un sumador                                                                   |

| de alta velocidadKL-33003(A)                                                                                          |

| d. Circuito de sumador de código BCDKL-33004(B)                                                                       |

| (10) Circuito de substractor media y substractor completa                                                             |

| a. Circuito de Substractor construido con puerta lógica                                                               |

| básicaKL-33004(A)                                                                                                     |

| b. Circuito de Sumador completo e inversorKL-33004(B)                                                                 |

| (11) Circuito de unidad de airmético lógica (ALU)                                                                     |

| KL-33003(B)                                                                                                           |

| (12) Circuito de generator de paridad de bit                                                                          |

| a. Generador de paridad de bit construido con puerta XOR                                                              |

| KL-33004(A)                                                                                                           |

| b. IC de Generaodr de paridad de bitKL-33003(D)                                                                       |

| (13) Circuito de codificador                                                                                          |

| a. Construcción de codificador 4 a 2 con puerta básica                                                                |

| KL-33005(A)                                                                                                           |

|                                                                                                                       |

| b. Construcción de codificador 10 a 4 con TTL IC                                                                      |

| KL-33006(A)                                                                                                           |

| KL-33006(A) (14) Circuito de decodificación                                                                           |

| KL-33006(A)  (14) Circuito de decodificación  a. Construcción de decodificación 2 a 4 con puerta básica               |

| KL-33006(A)  (14) Circuito de decodificación  a. Construcción de decodificación 2 a 4 con puerta básicaKL-33005(C)    |

| KL-33006(A)  (14) Circuito de decodificación  a. Construcción de decodificación 2 a 4 con puerta básica               |

c. BCD a decodificador de 7 segmentos..KL-33005(B)

22 736 3650 / 22 736 5827 22 736 4461 / 22 728 6162 systelec@systelec.cl

systelec@systelec.cl ww.systelec.cl

+56 9 34415419

Av. Pedro Fontova 3954 Santiago de Chile

| (  | (15) | Circuito de multiplexor                                                |

|----|------|------------------------------------------------------------------------|

|    |      | a. Construcción de multiplexor 2 a 1KL-33006(E)                        |

|    |      | b. Utilizando el multiplexor para crear funciones                      |

|    |      | KL-33006(F)                                                            |

|    |      | c. Construcción de multiplexor 8 a 1 con TTL IC                        |

|    |      | KL-33006(F)                                                            |

| (  | (16) | Circuito de demultiplexor                                              |

|    |      | a. Construcción de demultiplexor de salida 2                           |

|    |      | KL-33006(E)                                                            |

|    |      | b. Construcción de demultiplexor de salida 8                           |

| (  | \    | KL-33006(B)                                                            |

|    | (17) | Circuito de controlador análogo digital de multiplexor / demultiplexor |

|    |      | a. Características de interruptor análogo                              |

|    |      | KL-33006(C.D)                                                          |

|    |      | b. Transmisión bidireccional con interruptor análogo                   |

|    |      | CMOSICKL-33006(C)                                                      |

| 3. |      | perimentos del Circuito de Generador de Reloj                          |

|    | (1)  | Construcción de circuito de oscilador con puerta lógica                |

|    |      | básicaKL-33007(A)                                                      |

|    | (2)  | Construcción de circuito de oscilador con puerta schmitt               |

|    |      | KL-33007(B)                                                            |

|    | (3)  | Circuito de Oscilador controlado por voltaje (VCO)                     |

|    |      | KL-33007(C)                                                            |

|    | (4)  | Circuito de oscilador IC 555                                           |

|    |      | a. Circuito de oscilador 555KL-33007(D)                                |

|    | (=)  | b. Circuito VCOKL-33007(D)                                             |

|    | (5)  | Circuitos de multivibrador monoestable                                 |

|    |      | a. Circuitos de multivibrador monoestable de baja velocidad            |

|    |      | KL-33007(E)                                                            |

|    |      | b. Circuitos de multivibrador monoestable de alta velocidad            |

|    |      | c. Construcción de circuito de multivibrador monoestable               |

|    |      | KL-33007(D)                                                            |

|    |      | d. Construcción de circuito no retrigerable con TTL-IC                 |

|    |      | KL-33007(F)                                                            |

|    |      | e. Construcción de circuito retrigerable con TTL-IC                    |

|    |      | KL-33007(G)                                                            |

|    |      | f. Construcción de circuito oscilador de trabajo variable              |

|    |      | con multivibrador monoestableKL-33008(A)                               |

| 4. | Exr  | perimentos del Circuito de Lógica Secuencial                           |

|    |      | Circuitos flip-flop                                                    |

|    | ( )  | a. Construcción flip-flop R-S con puerta lógica básica                 |

|    |      | KL-33008(D)                                                            |

|    |      | b. Construcción flip-flop D con flip-flop R-S                          |

|    |      | KL-33008(D)                                                            |

|    |      | c. Construcción flip-flop J-K cib flip-flop D                          |

|    |      | KL-33008(D)                                                            |

|    |      | d. Construcción flip-flop J-K con flip-flop R-S                        |

|    |      | KL-33008(D)                                                            |

|    |      | e. Construcción de registro de desplazamiento con flip-flop D          |

|    |      | KL-33008(C)                                                            |

|    |      | f. Presione registro de desplazamiento izquierda / derecha             |

|    |      |                                                                        |

| (2) Circuitos de flip-flop J-K  a. Contador ascendente de Asincronía binariaKL-33009(A)                                                          |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---|

| b. Contador ascendente de Asincronía de década<br>KL-33010(D)                                                                                    |   |

| c. Contador ascendente de Asincronía dividido por N<br>KL-33010(C)                                                                               |   |

| d. Contador descendente de Asincronía binaria<br>KL-33009(A)                                                                                     |   |

| e. Contador ascendente de Sincronía binaria<br>KL-33009(A)                                                                                       |   |

| f. Contador ascendente / descendente de Sincronía binariaKL-33009(A)                                                                             |   |

| g. Contador ascendente / descendente de Sincronía binaria preestableKL-33010(A)                                                                  |   |

| h. Contador ascendente / descendente de Sincronía decimal preestable                                                                             |   |

| j. Contador Johnson'sKL-33009(A) 5. Experimentos del Circuito de Memoria                                                                         |   |

| (1) Construcción de memoria de solo lectura (ROM) con diodosKL-33010(F)                                                                          |   |

| (2) Construcción de memoria de acceso aleatorio (RAM) con flip-flop DKL-33010(G                                                                  |   |

| (3) Circuito RAM de 64 bitKL-33011(B) (4) Circuito de memoria de solo lectura programable borrable (EEPROM)KL-                                   |   |

| 33010(E)                                                                                                                                         |   |

| (5) Circuito electrónica EPROM (EEPROM)KL-33011(A) (6) Construcción de contador dinámica de escanéo con                                          |   |

| microprocesador de chip singularKL-33012(A) 6. Experimentos del Circuito Convertirdor (1) Circuito de conversor digital / análogo (DAC)          | ) |

| a. Circuito DAC unipolarKL-33013(A) b. Circuito DAC bipolarKL-33013(A)                                                                           |   |

| (2) Circuito de conversor digital / análogo (ADC) a. Circuito de conversor de 8 bitKL-33012(B) b. Circuito de conversor de 3 ½ dígitoKL-33013(B) |   |

| Accesorios(K1-38002)                                                                                                                             |   |

## Accesorios (KL-38002)

- 1. Manual de experimento y manual de instructor

- 2. Cables y enchufes de conexión : 1 juego

- 3. Llave : 1 pza.

### • Entrenamiento basado en computadora

- 1. Simulación de circuitos incorporados de módulos experimentales.

- 2. Se permite la simulación de fallas.

- 3. Los usuarios pueden comparar flexiblemente el resultado del análisis de simulación con salida de señal de hardware.

- 4. Soporte el instrumento virtual

g. Construcción de circuito de eliminación de ruido con flip-flop R-S.....KL-33008(D)